1. Процессор. Назначение, функции, основные блоки. Регистры процессора, классификация. Основные характеристики процессора.

Микропроцессор (Процессор) любой ядро микропроцессорной системы, m.ĸ. именно ОН всю обработку информации ней. производит Микропроцессоры то же что и процессоры только маленькие. Микропроцессор – это микроэлектронное программируемое устройство, предназначенное обработки информации управления u процессами обмена этой информацией составе микропроцессорной системы (компьютера).

Основные функции процессора:

- 1. Дешифрация и выполнение команд программы;

- 2. Организация обращения к оперативной памяти;

- 3. Организация обращения к устройствам ввода-вывода (УВВ);

- 4. Прием и обработка запросов от устройств вычислительной системы (ВС) и внешней среды (запросов на прерывание).

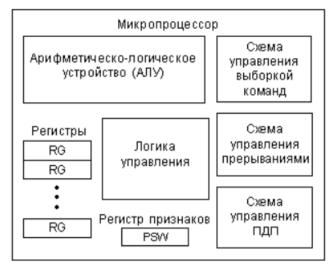

Обязательными компонентами микропроцессора являются регистры, арифметико-логическое устройство (АЛУ) и блок управления.

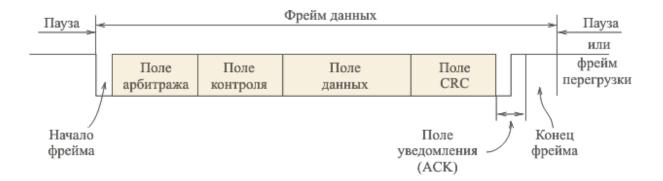

Структура процессора показана на рис.4.

Рис. 4

Блок управления отвечает за последовательное выполнение команд программы, правильное перенаправление потоков данных и взаимодействие узлов процессора. Содержит следующие элементы:

- 1. Схема управления выборкой команд (выборка команд из памяти и их дешифрация);

- 2. Схема управления прерываниями (обрабатывает поступающий процессор запрос прерывания, на обработки определяет agpec начала программы прерывания, сохраняет в памяти текущее состояние процессора и обеспечивает регистров nepexog программе обработки прерывания);

- 3. Схема управления прямым доступом к памяти (ПДП, DMA Direct Memory Access) (отключает процессор от внешних шин на время предоставления прямого доступа к памяти запросившему его устройству);

- 4. Логика управления (Организует взаимодействие узлов процессора, синхронизирует работу процессора с внешними сигналами и реализует обмен данными между процессором и памятью или устройствами ввода-вывода);

Арифметико-логическое устройство. Отвечает за выполнения арифметических и логических операций (т. е. для обработки данных)в соответствии с командой, дешифрированной блоком управления.

Регистры предназначены для временного хранения данных, адресов и специальных кодов в целях сокращения количества обращений к медленной ОП.

# Классификация регистров:

- 1. Функциональные регистры

- а) Регистры общего назначения (РОН) (запоминают операнды и результаты операций);

- б) Специальные регистры (Только для вычисления адресов. Счетчик команд это спец. регистр);

- в) Индексные (помнят номера элементов массивов);

- г) Регистры-указатели (указывают на начало некоторой области памяти. Пример: указатель стека);

- g) Регистр флагов (его биты содержат информацию о результате предыдущей команды);

- 2. Системные регистры

- а) Управляющие регистры (Задают режимы работы процессора, кэш-памяти и т.д.);

- б) Регистры системных адресов (помнят специальные адреса, например, адреса таблиц дескрипторов при виртуальной организации памяти);

- 3. Вспомогательные регистры

- а) Теневые регистры (используются при виртуальной организации памяти для хранения дескрипторов с целью сокращения числа обращений к памяти);

- б) Регистры отладки и тестирования;

- в) Буферные регистры;

- г) Стеки

# Основные характеристики процессора:

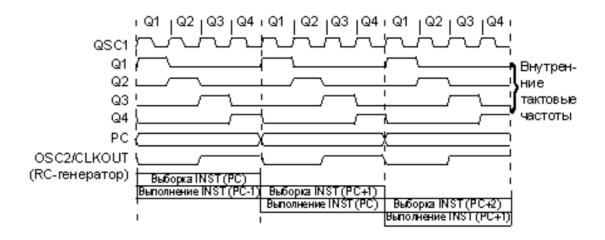

- 1. Тактовая частота (зачастую процессор в разы быстрее остальных элементов системы, поэтому используется внешняя и внутренняя тактовые частоты. Внешняя частота системной шины, для синхронизации обмена данных между процессором и другими устройствами. Внутренняя частота синхронизации самого процессора);

- 2. Разрядность данных (Тоже есть внешняя и внутренняя. Внешняя число бит, которое за один раз можно передать между процессором и другими устройствами. Внутренняя число бит, которое процессор может обрабатывать одновременно);

- 3. Адресное пространство (совокупность ячеек памяти ПЗУ, ОЗУ и устр. I/O. Максимальный объём = 2^n, где n разрядность шины адреса);

- 4. Система команд и способы адресации (все команды, выполняемые процессором);

- 5. Система прерываний;

- 2. Классификация микропроцессоров по архитектуре, по области применения, по типу управления, по производительности и стоимости.

# Классификация микропроцессоров:

- 1. По архитектуре (архитектура функциональная организация, в которую закладываются основные идеи и принципы для достижения наивысшей производительности)

- 1.1. По степени полноты системы команд:

- a) CISC (Complex Instruction Set Computer);

- 6) RISC (Reduced Instruction Set Computer).

- 1.2. По общему структурному составу:

- а) Скалярные процессоры (в АЛУ одновременно за одну команду могут обрабатываться 1-2 операнда);

- б) Векторные процессоры (По одной команде обрабатывается множество операндов, которые называют вектором или матрицей операндов);

- в) Суперскалярные процессоры (Строятся на базе нескольких параллельно работающих АЛУ. Ресурсы распределяются динамически);

- г) VLIW (Very Long Instruction Word, очень командное (Tom длинное слово) суперскалярный, НО ресурсы процессора который компилятором, распределяются группирует команды длинные командные В слова со многими кодами операций).

- 2. По областям применения:

- а) Универсальные процессоры (для решения широкого круга задач);

- б) Микроконтроллеры (для построения устройств управления различной аппаратурой);

- в) Цифровые процессоры обработки сигналов (для цифровой обработки аналоговых сигналов);

- г) Медийные процессоры (для преобразования графической и звуковой информации);

- 3. По muny управления

- а) Асинхронные (устройство управления рассылает по блокам процессора приказы и принимает от них ответные сигналы об окончании заданной работы);

- б) Синхронные (Устройство управления рассылает по блокам приказы и не ожидает ответных сигналов. Блоки выполняют заданные действия в течение фиксированного, заранее известного интервала времени);

- 4. По производительности и стоимости

- а) Низкая (для встроенных систем);

- б) Средняя (для ПК);

- в) Высокая (для рабочих станций, серверов, суперкомпьютеров).

- 3. Использование микропроцессоров в системах управления. Структурная схема системы на базе микропроцессора.

#### (Сделал полностью в GPT тк нет информации нигде)

Микропроцессоры широко используются в системах своей вдовогодоря управления высокой производительности гибкости. Они u **MOSYM** обрабатывать большой объем данных и выполнять сложные алгоритмы управления в режиме реального Примеры применения времени. микропроцессоров системах управления:

- 1. Автоматические системы контроля и управления производственными процессами, такие как управление температурой, давлением, скоростью и т.д.

- 2. Системы управления транспортными средствами, такие как автоматические тормозные системы, системы контроля стабильности и т.д.

- 3. Системы управления энергетическими процессами, такие как управление энергоснабжением, солнечными батареями и т.д.

- 4. Системы управления домашними устройствами, такие как умный дом, умный кондиционер и т.д.

- 5. Системы управления роботами и автоматическими машинами, такие как промышленные роботы, автоматические станки и т.д.

Микропроцессоры обеспечивают точность и надежность в системах управления, что позволяет снизить затраты на обслуживание и повысить эффективность работы системы

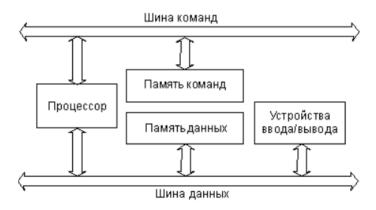

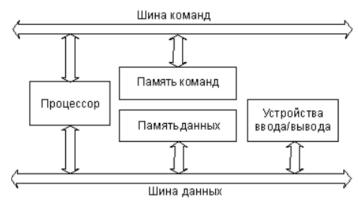

Структурная схема системы на базе микропроцессора обычно включает в себя следующие блоки:

- 1. Микропроцессор (CPU) является сердцем системы и отвечает за обработку данных и выполнение команд.

- 2. Память (RAM, ROM, EEPROM) используется для хранения программного кода и данных.

- 3. Внешние устройства ввода-вывода (клавиатура, мышь, дисплей, принтер, датчики и т.д.) используются для взаимодействия с пользователем и получения данных из внешней среды.

- 4. Контроллеры периферийных устройств (DMA, UART, SPI и т.д.) управляют передачей данных между микропроцессором и внешними устройствами ввода-вывода.

- 5. Интерфейсы для связи с другими устройствами (Ethernet, USB, RS-232 и т.д.) используются для обмена данными между системой и другими устройствами.

- 6. Часы реального времени (RTC) используются для хранения и управления временем и датой в системе.

- 7. Питание и управление энергопотреблением управляют питанием системы и устройствами ввода-вывода для уменьшения энергопотребления.

- 8. Интерфейсная шина для связи между блоками системы (например, шина данных и адресов).

- 9. Система прерываний используется для управления операциями системы и взаимодействия с внешними устройствами.

- 10. ПО системы программный код для управления системой и взаимодействия с пользователем.

Структурная схема системы на базе микропроцессора может отличаться в зависимости от конкретного устройства и его функциональности.

Микроконтроллеры. Разрядность микроконтроллеров.

Основные семейства 8- разрядных микроконтроллеров.

Архитектуры – гарвардская и фон-неймановская;

открытая и закрытая; RISC и CISC.

МК можно классифицировать

# 1) <u>по разрядности данных</u>:

- 8-ми разрядные МК (наиболее многочисленная группа. Это простые и дешевые МК с относительно низкой производительностью)

- 16-ти разрядные МК (модификация 8-ми разрядных. Характеризуются расширенной системой команд и способов адресации, увеличенным набором регистров и объемом адресуемой памяти)

- 32-х разрядные МК (есть высокопроизводительный процессор, почти такой как у процессоров общего назначений)

# 2) По шинной организации:

- архитектура с общей, единой шиной для данных и команд (одношинная, или принстонская, фон-неймановская архитектура).

**Достоинство**: наличие единой памяти данных и команд позволяет гибко распределять ее объем между кодами данных и команд.

- альтернативный тип архитектуры микропроцессорной системы — это архитектура с раздельными шинами данных и команд (двухшинная, или гарвардская, архитектура). Обмен процессора с каждым из двух типов памяти происходит по своей шине. Достоинство: возможность одновременной выборки команд и данных.

# 3) По архитектуре

а) <u>CISC</u> (До конца 70-х годов прошлого века полагалось, что производительность процессора тем выше, чем мощнее его система команд. В результате процессоры CISC развивались за счет расширения микрокода и усложнения операций)

Особенности CISC-процессоров:

- 1. Поддержка большого количества команд и способов адресации;

- 2. Реализация сложных команд на аппаратном уровне;

- 3. Различные команды имеют различную длительность исполнения;

- 4. Многие команды могут обращаться к ОП;

- 5. Небольшой объем регистровой памяти (8 16 регистров общего назначения).

# Достоинства:

- выполнение сложных операций одной командой;

- возможность выполнять обработку данных непосредственно в OП.

# Недостатки:

- переменная длительность исполнения различных команд требует построения сложных асинхронных конвейеров;

- исполнение многих команд требует обращения к медленной ОП;

- малый объем регистровой памяти приводит к частым обращениям к ОП.

- б) <u>RISC</u> (В процессорах с RISC-архитектурой реализована идея о том, что производительность

процессора напрямую зависит от простоты команд, которая возникла в 80-х годах прошлого века. В RISC-архитектуре аппаратно реализовали 20% (от команд CISC) самых используемых команд, а остальные 80% вынесли на программный уровень.)

#### Особенности RISC-процессоров:

- 1. Все команды разделены на 2 группы:

- команды обмена с памятью;

- команды обработки данных (Команды обработки данных работают только с регистрами. Вначале данные должны быть записаны в регистры с помощью команд первого типа, и только затем над ними выполняется операция с помощью команд второго типа.).

- 2. Команды имеют фиксированный формат и длительность исполнения;

- 3. Большой объем регистровой памяти (десятки и сотни РОН).

#### Достоинства:

- фиксированная длительность исполнения команд позволяет строить более простые синхронные конвейеры;

- сокращение количества обращений к памяти снижает требования к ее пропускной способности;

- более короткий цикл разработки процессора, чем y CISC;

- простота RISC-процессора позволяет высвободить площадь кристалла для реализации дополнительных структур, увеличивающих производительность (больше РОН, кэш и т.д.)

# Недостатки:

- программа для RISC-процессора содержит большее количество команд, чем аналогичная программа для CISC процессора.

<u>Закрытая архитектура</u> – отсутствие линий ША и ШД на выводах корпуса МК.

<u>Открытая архитектура</u> - наоборот.

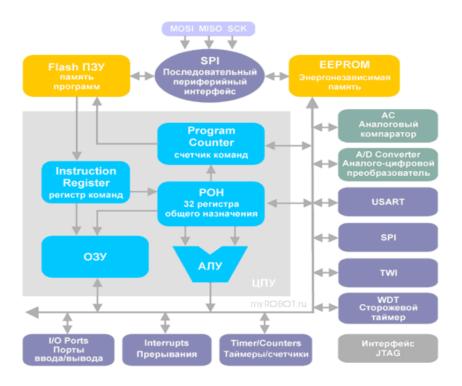

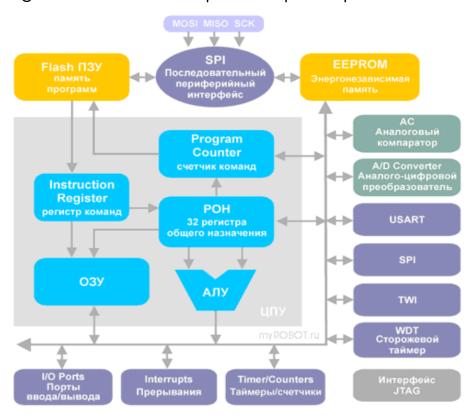

5. Обобщенная структурная схема микроконтроллера. Основные блоки. Память программ и данных. Виды ПЗУ, применяемые для памяти программ.

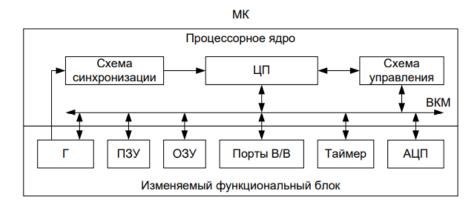

Модульный принцип построения МК: МК одного семейства содержат базовый функциональный блок (Процессорное ядро), одинаковый для всех МК данного семейства, и изменяемый функциональный блок, который отличается в МК разных моделей в пределах семейства.

Процессорное ядро включает:

- ЦП;

- внутренние магистрали адреса, данных и управления (внутриконтроллерные магистрали, ВКМ);

- схему формирования импульсной последовательности для тактирования ЦП и межмодульных магистралей;

- устройство управления режимами работы МК: состояние начального запуска (сброс), активный режим, в котором МК выполняет прикладную программу, режимы пониженного энергопотребления.

Изменяемый функциональный блок включает:

- модули различных типов памяти;

- модули генераторов синхронизации (Г);

- модули периферийных устройств (таймеры, параллельные порты ввода/вывода, АЦП, ЦАП, контроллеры ЖК-индикаторов и др.)

В простых МК модуль обработки прерываний входит в состав процессорного ядра. В более сложных МК он представляет собой отдельный модуль.

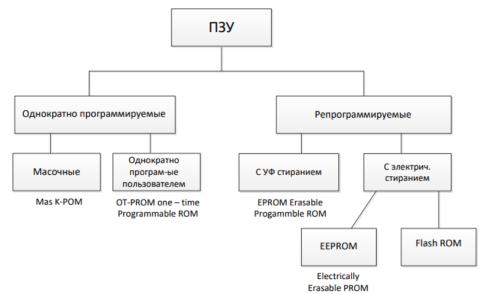

В МК используется три основных вида памяти.

- память программ ПЗУ, предназначена для хранения программного кода (команд) и констант. Ее содержимое в ходе выполнения программы не изменяется;

- память данных ОЗУ, предназначена для хранения переменных в процессе выполнения программы;

- регистры МК внутренние регистры ЦП и регистры управления периферийными устройствами (регистры специальных функций).

#### Память программ

Все ПЗУ представленные ниже являются энергонезависимыми.

# 1. ПЗУ масочного muna (mask-ROM).

Информация заносится в память при ее изготовлении и не может быть впоследствии изменена.

Достоинство: высокая надежность хранения информации, дешевизна при больших объемах производства.

Недостаток: изменение программы требует новой серии МК. Выпуск памяти такого типа целесообразен только в случае массового производства.

2. Однократно программируемые пользователем ПЗУ – OTPROM (One Time Programmable ROM).

В незапрограммированном состоянии каждая ячейка памяти при считывании возвращает код \$FF. Программируются те разряды, которые должны

содержать 0. После установки в 0 разрядов ячейки невозможно восстановить их единичное значение. Это возможно за счет многократного приложения импульсов повышенного напряжения к битам ячейки памяти.

3. Репрограммируемые ПЗУ с ультрафиолетовым стиранием – EPROM (Erasable Programmable ROM).

каждым сеансом программирования дΛя единичных значений весь модуль восстановления подвергается стиранию npu помощи ультрафиолетового облучения. Для этого корпус МК выполнен со специальным стеклянным окном. Число сеансов стирания/программирования составляет 25-100 раз. МК с таким ПЗУ стоят дорого.

4. Репрограммируемые ПЗУ с электрическим стиранием – EEPROM (Electrically Erasable Programmable ROM).

Стирание ячеек памяти производится электрическими сигналами. Дешевле, чем EPROM, но дороже, чем ОТРROM. Максимальное число циклов стирания/программирования равно 10000.

Достоинство: возможность стирать и программировать МК, не снимая его с платы, что позволяет производить отладку и модернизацию ПО.

Используются редко, т.к. Flash-ПЗУ дешевле и имеют сходные характеристики

5. ПЗУ с электрическим стиранием типа Flash – Flash-ROM.

Отличается от EEPROM способом стирания информации. В EEPROM стирание производится отдельно для каждой ячейки, а во Flash-памяти стирать можно только блоками или страницами. Страница составляет 8, 16 или 32 байта. Стоимость не намного выше, чем ОТРКОМ.

В современных МК используется два типа ПЗУ: Flash-ROM – для хранения программ, EEPROM – для хранения перепрограммируемых констант (настроек пользователя). Пример: запоминание каналов в музыкальных центрах и телевизорах. Число циклов стирания/программирования Flash-ROM равно 105.

Наиболее совершенные МК содержат: ПЗУ программ muna Flash-ROM, масочное ПЗУ монитора связи, EEPROM ПЗУ для хранения изменяемых констант и ОЗУ данных.

#### Память данных

Как правило, выполняется на основе статического ОЗУ. Содержимое ячеек ОЗУ сохраняется при снижении тактовой частоты МК до сколь угодно малых значений, что позволяет снизить энергопотребление.

Информация сохраняется В памяти данных напряжении питания не ниже напряжения хранения информации - U\_STANDBY (обычно около 1 снижении напряжения ниже минимально допустимого уровня U\_DDMIN, но выше уровня U\_STANDBY выполнение программы МК прекращается, но информация в ОЗУ сохраняется. При восстановлении напряжения питания сброс MK, выполнение npoucxogum u программы продолжается без потери данных.

Объем памяти данных обычно составляет десятки и сотни байт, поэтому в некоторых случаях возникает необходимость подключения дополнительной внешней памяти (как памяти программ, так и данных).

6. Порты ввода-вывода микроконтроллеров. Виды портов; структурная схема одного разряда параллельного порта с альтернативной функцией.

# Параллельные І/О порты

Каждый MK некоторое линий имеет количество ввода/вывода, которые объединены в многоразрядные (чаще 8-разрядные) параллельные порты ввода/вывода. В MK памяти каждому ввода/вывода nopmy coombemcmbyem свой agpec pezucmpa данных. Обращение к регистру данных порта ввода/вывода производится теми же командами, что и обращение к памяти данных.

В зависимости от реализуемых функций различают следующие типы параллельных портов:

- однонаправленные порты, предназначенные только для ввода или только для вывода информации;

- двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации МК;

- порты альтернативной функцией С (мультиплексированные порты). Отдельные линии этих используются совместно со встроенными периферийными устройствами MK, такими как таймеры, АЦП. контроллеры последовательных интерфейсов;

- порты с программно управляемой схемотехникой входного/выходного буфера.

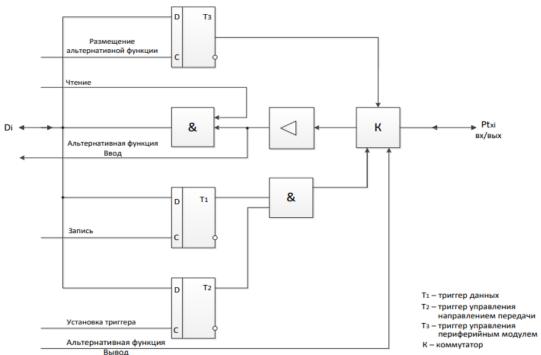

Схема управления одним разрядом параллельного порта двунаправленного ввода вывода с альтернативной функцией

В режимах записи и чтения триггер Т3 должен быть установлен в «0», тем самым коммутатор подключает порт Рtxi к линии входа/ выхода микроконтроллера Di Триггер управления Т2 разрешает вывод данных на внешний вывод.

Если Т2 находится в нуле, то разрешается ввод данных. При этом считывается значение сигнала, поступающее с входа/ выхода Ptxi по сигналу «чтения» на линию Di. (а не содержимое триггера T1).

Если Т2 в единице, то контакт Ptxi порта применяется для вывода данных и по сигналу «запись» на выход подается предварительно записанный бит из триггера Т1.

В современных МК, как правило, обеспечивается индивидуальный доступ к триггерам данных и управления, что позволяет использовать каждую линию порта независимо в режиме ввода или вывода путем установки триггера Т2.

Для разрешения обмена периферии микроконтроллера с внешним объектом триггер Т3 необходимо установить в «1». При этом коммутатор подключает порт Ptxi к линиям входа/ выхода периферийного устройства.

# Последовательные І/О порты

Задачи, которые решаются средствами модуля контроллера последовательного ввода/вывода, можно разделить на три основные группы:

- 1. Связь встроенной микроконтроллерной системы с системой управления верхнего уровня, например, с персональным компьютером. Чаще всего для этой цели используются интерфейсы RS-232C и RS-485;

- 2. Связь с внешними по отношению к МК периферийными ИС, а также с датчиками физических величин с последовательным выходом. Для этих целей используются интерфейсы I2C (Inter-Integrated Circuit), SPI (Serial Peripheral Interface), а также нестандартные протоколы обмена;

- Интерфейс 3. связи локальной С сетью В мультимикроконтроллерных системах. В системах с числом МК до пяти обычно используются сети на основе интерфейсов I2C, RS-232C и RS-485 с собственными сетевыми протоколами ВЫСОКОЗО уровня. В сложных системах все более популярным становится протокол CAN (Controller Area Network).

- С точки зрения организации обмена информацией упомянутые типы интерфейсов последовательной связи отличаются:

- 1) режимом передачи данных (синхронный или асинхронный)

- 2) форматом кадра (число бит в посылке при передаче байта полезной информации)

- 3) временными диаграммами сигналов на линиях (уровни сигналов и положение фронтов при переключениях)

- 4) режимом обмена информацией: симплексный (om simplex простой), дуплексный, полудуплексный (om duplex двойной);

- 5) числом линий, по которым происходит передача в последовательном коде, обычно равно двум (I2C, RS-232C, RS-485) или трем (SPI).

Mogynu контроллеров последовательных интерфейсов реализуют на аппаратном уровне логику протоколов обмена заданных интерфейсов. Одноименные модули для различных МК даже одного семейства могут иметь отличия с точки аппаратной реализации, но протоколы обмена должны обеспечиваться coombemcmbuu выбранным В С стандартом.

#### короткие вопросы

Какая архитектура процессора называется гарвардской?

Это архитектура с раздельными шинами данных и команд

(Обмен процессора с каждым из двух типов памяти происходит по своей шине. **Достоинство**: возможность одновременной выборки команд и данных.)

2. Какая архитектура процессора называется фон-неймановской?

Это архитектура с общей, единой шиной для данных и команд

(Достоинство: наличие единой памяти данных и команд позволяет гибко распределять ее объем между кодами данных и команд.)

3. Для чего в состав микроконтроллеров входит счетчик-таймер?

Для эффективного решения задач отсчёта равных интервалов времени, измерения длительности сигнала, подсчёта числа импульсов на временном интервале, формирования на линии вывода сигнала с задержкой или определенной частотой.

4. Для чего нужен такое сторожевой таймер?

На случай выхода из состояния на котором завис МК.

(Он сбрасывается устройством через равные промежутки времени, а если в течение некоторого периода времени сброса не было, то таймер делает вывод, что система зависла, и перегружает ее.)

7. Таймеры в микроконтроллерах. Основные функции; режимы работы. Функциональная схема простого счетчика-таймера. Измерение временного интервала; временные диаграммы. Недостатки простого таймера.

Для эффективного управления в режиме реального времени МК должен решать следующие задачи:

- отсчет равных интервалов времени заданной длительности, повтор алгоритма управления по истечении каждого такого интервала (обычно эту функцию называют формированием меток реального времени);

- измерение длительности сигнала на линии ввода;

- nogcчет числа импульсов внешнего сигнала на заданном временном интервале;

- формирование на линии вывода сигнала заданного логического уровня с программируемой задержкой по отношению к изменению сигнала на линии ввода;

- формирование на линии вывода импульсного сигнала с программируемой частотой и коэффициентом заполнения.

Решение перечисленных задач программным путем без использования аппаратных средств является неэффективным, так как занимает ресурсы, необходимые для вычислений. Поэтому для решения задач управления в 5 реальном времени используют специальные аппаратные средства, которые называют таймерами.

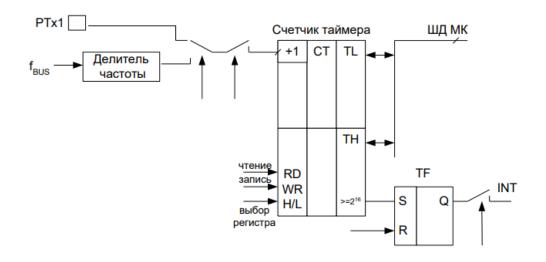

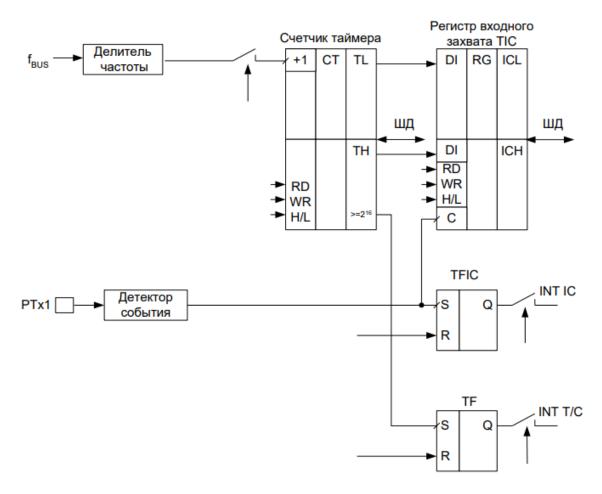

Типичный таймер представляет собой 16-разрядный счетчик со схемой /правления (Рис. 8).

Рис. 8

В памяти МК счетчик отображается двумя регистрами: TH – старший байт счетчика, TL – младший

байт. Регистры доступны для чтения и для записи. Направление счета – только прямое, (т.е. при поступлении входных импульсов содержимое счетчика инкрементируется).

- В зависимости от настройки счетчик может использовать один из источников входных сигналов:

- импульсную последовательность с выходо управляемого делителя частоты fBUS (режим таймера);

- внешнюю импульсную последовательность, поступающую на один из входов МК (режим счетчика событий).

При переполнении счетчика устанавливается триггер переполнения ТF, который генерирует запрос на прерывание, если прерывания от таймера разрешены.

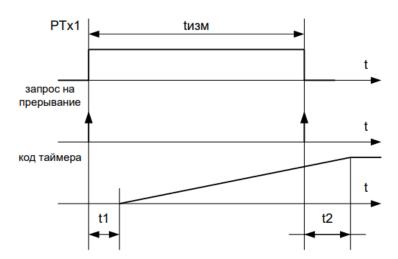

- 1. прерывается выполнение текущей программы при изменении сигнала на линии PTx1 с 0 на 1; в подпрограмме прерывания устанавливается регистр счетчика таймера в 0 и разрешается счет;

- 2. при изменении сигнала на линии с 1 на 0 еще раз прерывается выполнение программы; в п/п прерывания останавливается счет; код в регистрах счетчика будет равен длительности интервала, выраженной числом периодов частоты тактирования счетчика.

Моменты разрешения и остановки счета t1 и t2 не совпадают с моментами изменения сигнала на входе PTx1, так как пуск и останов выполняются в п/п прерывания. Ошибка счета равна t1-t2. Каждое из значений t1 и t2 определяется временем перехода МК к

выполнению п/п прерывания и временем выполнения некоторого числа команд. Максимальная ошибка может составить несколько десятков мкс, поэтому рассмотренный метод не может быть использован для измерения интервалов микросекундного диапазона.

Еще одним недостатком простейшего таймера-счетчика является невозможность формировать метки реального времени с периодом, отличным от периода полного коэффициента счета, равного 216.

Эти недостатки устранены в усовершенствованном модуле таймерасчетчика, используемом в МК семейства МСS-51.

Реализован аппаратный пуск и останов таймера – это повышает точность измерения временных интервалов, так как интервалы t1 и t2 не являются 7 составляющими погрешности измерения.

Реализован режим перезагрузки счетчика произвольным кодом в момент переполнения – это позволяет формировать метки реального времени с периодом, отличным от периода полного коэффициента счета.

Главным недостатком модуля типичного таймера-счетчика является невозможность одновременного обслуживания нескольких каналов. Увеличение числа каналов производят следующими способами:

- увеличение числа модулей таймеров-счетчиков. Примеры: МК семейства MCS-51, МК компаний Mitsubishi и Hitachi;

- введение в структуру таймера-счетчика дополнительных аппаратных средств: канала входного захвата (Input Capture IC) и канала выходного сравнения (Output Compare OC).

- 8. Счетчик-таймер с каналом входного захвата. Функциональная схема. Измерение временного интервала; временные диаграммы.

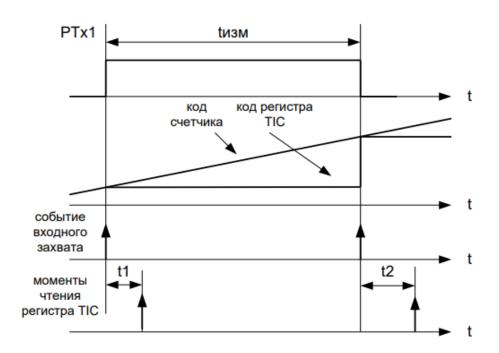

Детектор событий следит за уровнем напряжения на одном из входов МК (рис. 10). Обычно это одна из линий порта в/в. При изменении уровня логического сигнала детектор события вырабатывает строб записи, и текущее состояние счетчика-таймера записывается в 16-разрядный регистр входного захвата ТІС. Это называется событием захвата. Возможны следующие варианты событий захвата:

- изменение логического сигнала с 0 на 1 (передний фронт сигнала);

- изменение логического сигнала с 1 на 0 (задний фронт входного сигнала);

- любое изменение логического уровня сигнала

Измерение временного интервала с помощью канала входного захвата показано на рис. 11. При изменении уровня входного сигнала с 0 на 1 код счетчика

K1 pesucmp TIC. Tpussep TFIC копируется В Формируется 1. устанавливается В запрос на (таймер сообщает МК, прерывание что интервал задержкой t1 MK считывает начался). С код К1 TIC, сбрасывает mpuzzep TFIC pezucmpa инициализирует детектор событий на контроль 30 PTx1. фронтом CUSHQVQ При падающим изменении сигнала с 1 на 0 детектор снова фиксирует событие захвата, и код счетчика K2 копируется в регистр TIC. Снова выставляется запрос на прерывание. С задержкой t2 код считывается в память МК. Разность кодов К2-К1 и есть длительность измеряемого интервала

Достоинство: текущее состояние счетчика сохраняется аппаратными средствами, поэтому исключаются ошибки измерения входного интервала времени, связанные CO временем nepexoga К подпрограмме обработки прерывания.

Недостаток: содержимое регистра входного захвата после первого события должно быть считано МК до того, как произойдет второе событие захвата. Время перехода к п/п обработки прерывания

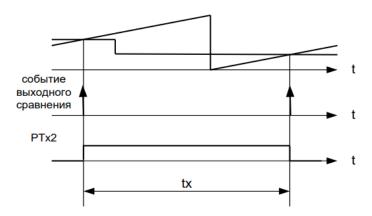

9. Счетчик-таймер с каналом выходного сравнения. Функциональная схема. Формирование на выходе микроконтроллера временного интервала заданной длительности; временные диаграммы.

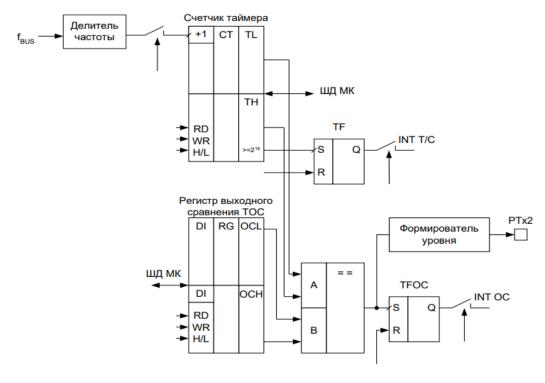

Компаратор сравнивает текущий код счетчика таймера с кодом, который записан в 16-разрядном регистре выходного сравнения ТОС (рис. 9.6). В момент равенства кодов на одном из выходов МК (РТх2) устанавливается заданный уровень логического сигнала. Рассмотренное действие называют событием выходного сравнения.

Возможны три типа изменения сигнала на выходе PTx2 в момент события выходного сравнения:

- установка высокого логического уровня;

- установка низкого логического уровня;

- инвертирование сигнала на выходе.

При наступлении события сравнения устанавливается в 1 триггер выходного сравнения ТГОС. Состояние триггера выходного сравнения может 10 быть считано программно. Если разрешены прерывания по событию сравнения, то формируется запрос на прерывание INT ОС.

Рис. 12

Канал выходного сравнения позволяет сформировать на выходе временной интервал заданной длительности tx.

Первое событие сравнения t1 В момент формирует нарастающий фронт PTx2. CUSHOVO Одновременно генерируется запрос на прерывание. В п/п прерывания происходит загрузка нового кода сравнения К2. Время, необходимое для записи нового значения в регистр сравнения ТОС, ограничивает длительность формируемого минимальную интервала. В момент t2 наступает второе событие, и выход РТх2 устанавливается в 0. Длительность

сформированного интервала tx определяется только разностью кодов. В отличие от типичного таймера, счетчик используется age непосредственно ΩΛЯ формирования измеряемого интервала, в усовершенствованном таймере счетчик лишь создает образ времени, подобно часам. Все действия по формированию или временных интервалов измерению производят аппаратные средства захвата и сравнения.

Поэтому счетчик в составе усовершенствованного таймера называют счетчиком временной базы.

Число каналов входного захвата и выходного сравнения в модуле усовершенствованного таймера МК может быть различным.

Для семейства HC05 Motorola типовыми решениями являются: 2IC+2OC или 1IC+1OC.

Усовершенствованный таймер позволяет решить многие задачи управления в реальном времени, но имеет следующие ограничения:

- недостаточное число каналов захвата и сравнения, принадлежащих одному счетчику;

- однозначно определенная конфигурация канала (или захват или сравнение)

# 10. Процессор событий. Структурная схема, режимы работы. Режим ШИМ, временная диаграмма.

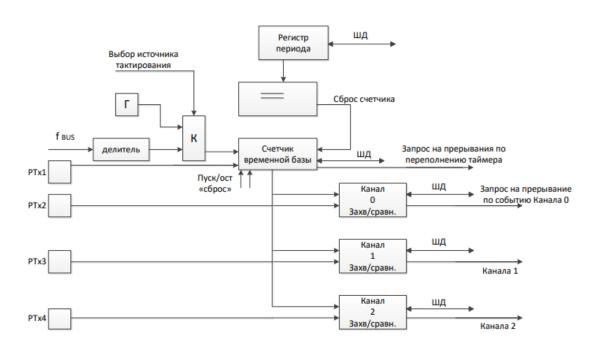

В процессорах событий устранены ограничения усовершенствованных таймеров. Процессоры событий были впервые использованы в МК семейства Intel 8xC51Fx.

Процессор событий в этом МК получил название программируемого счетного массива (Programmable Counter Array, PCA).

Процессор событий состоит из 16-разрядного счетчика временной базы и нескольких универсальных каналов захвата/сравнения.

Счетчик может тактироваться импульсной последовательностью с выхода делителя частоты или внешним генератором. Счетчик имеет опции пуска/останова и сброса в 0.

модели процессора событий Некоторые 12 коэффициента gonyckaюm изменение счета счетчика временной базы (изменение периода его работы). в составе Для osome модуля имеется двухбайтовый онммодѕодп доступный pesucmp периода и компаратор. При совпадении текущего кода счетчика с кодом периода триггеры счетчика автоматически сбрасываются в 0.

Режимы работы универсальных каналов:

- режим входного захвата

- режим выходного сравнения

- режим широтно-импульсной модуляции (ШИМ)

Первые два режима аналогичны режимам модуля усовершенствованного таймера. Каждый канал включает двухбайтовый регистр данных и триггер события. В зависимости от выбранного режима регистр данных используется для записи кода счетчика в момент наступления входного захвата или для хранения кода выходного сравнения. Триггер устанавливается при наступлении любого из этих событий.

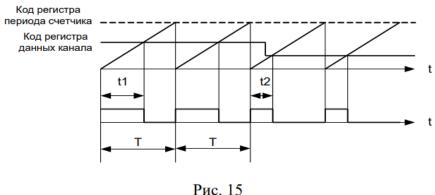

Рис. 15

В режиме ШИМ на соответствующем выводе МК формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы. Длительность импульса прямо пропорциональна коду в регистре данных канала.

Коэффициент заполнения  $\gamma = t1/T$ .

С помощью сигнала ШИМ осуществляется управление аналоговыми внешними устройствами, например, электродвигателями, светодиодами и т.д.

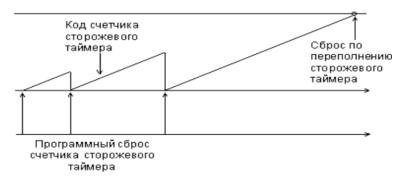

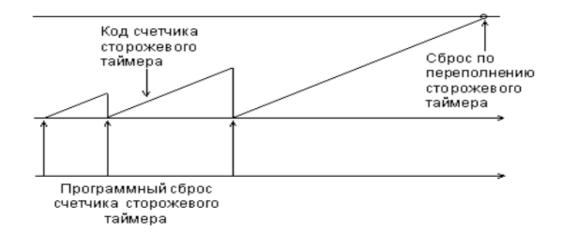

# 11. Сторожевой таймер: назначение, принцип работы. Пояснить временной диаграммой. Функциональная схема.

Если МК неожиданно "завис", то на случай выхода из этого состояния все современные контроллеры имеют встроенный модуль сторожевого таймера. Принцип действия сторожевого таймера показан на рис. 16

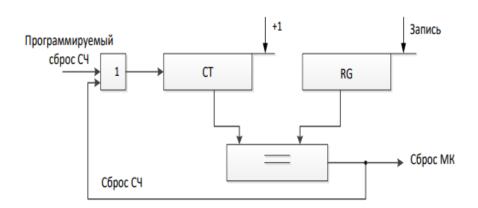

Структурная схема сторожевого таймера показана на рис 17. Максимальный код счетчика записывается в специальном регистре. Основу сторожевого таймера составляет многоразрядный счетчик.

При сбросе МК счетчик обнуляется. После перехода МК в активный режим работы значение счетчика начинает увеличиваться независимо от выполняемой программы. При достижении счетчиком максимального кода генерируется сигнал внутреннего сброса, и МК начинает выполнять рабочую программу сначала.

Для исключения сброса по переполнению сторожевого таймера рабочая программа МК должна периодически сбрасывать счетчик. Сброс счетчика сторожевого таймера осуществляется путем исполнения специальной команды (например, CLRWDT) или посредством записи некоторого указанного кода в один из регистров специальных функций. Тогда при

нормальном, предусмотренном разработчиком, порядке исполнения рабочей программы, переполнения счетчика сторожевого таймера не происходит, и он не оказывает влияния на работу МК. Однако, если исполнение рабочей программы было нарушено, например, вследствие "зависания", то велика вероятность того, что счетчик не будет сброшен вовремя. Тогда произойдет сброс по переполнению сторожевого таймера, и нормальный ход выполнения рабочей программы будет восстановлен. Сброс счетчика может осуществляться: 1) путем исполнения специальной команды; 2) периодически меняя значение регистра (рис. 17).

Модули сторожевых таймеров конкретных МК могут иметь различные особенности:

- в ряде МК векторы внешнего сброса и сброса по переполнению сторожевого таймера совпадают. Это не позволяет выявить причину сброса программным путем и затрудняет написание рабочей программы. Более высокоуровневые МК имеют либо различные векторы сброса, либо отмечают 1 СТ RG Сброс МК +1 Сброс СЧ Программируемый сброс СЧ Запись 15 событие сброса по переполнению сторожевого таймера установкой специального бита в одном из регистров специальных функций;

- в некоторых МК при переходе в один из режимов энергопотребления, озоннажиного когда рабочая программа выполняется, автоматически не приостанавливается работа сторожевого таймера. В других МК сторожевой таймер имеет независимый генератор, который тактовый продолжает функционировать и в режиме ожидания. В этом случае необходимо периодически выводить МК из состояния сброса сторожевого таймера. ожидания ΩΛЯ PIC-контроллерах фирмы Microchip выработка таких сбросов может быть запрещена путем записи нуля в специальный бит конфигурации WDTE.

На выполнение функций сторожевого таймера может быть запрограммирован один из универсальных каналов процессора событий.

Использование сторожевого таймера существенно повышает способность к самовосстановлению системы на основе МК.

# 12. Модуль аналогового ввода-вывода в составе микроконтроллера (АЦП). Функциональная схема, режимы работы.

Прикладная программа, записанная В память MK, должна обеспечивать eso надежное Однако функционирование. В результате электромогнитных nomex, колебаний напряжения питания и других внешних факторов могут произойти сбои в работе МК..С целью обеспечения надежного работы MK контроля u восстановления работоспособности системы в отсутствие оператора MK снабжаются современные аппаратными обеспечения работы. средствами надежной относятся:

- схема формирования сигнала сброса МК;

- модуль мониторинга напряжения питания;

- сторожевой таймер.

Необходимость приема и формирования аналоговых сигналов требует наличия в МК модулей аналогового ввода/вывода.

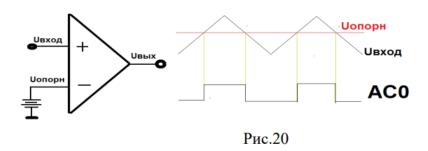

Простейшим устройством аналогового ввода в МК является встроенный компаратор напряжения. Основная функция компаратора – это сравнение двух напряжений, одно из которых образцовое или опорное, а другое собственно измеряемое. Выходной сигнал компаратора может принимать лишь два значения: логический ноль, и логическая же единица

Компараторы удобнее BCGSO использовать контроля определенного значения входного напряжения, например, В термостатах. Компаратором заряда батареи отслеживать уровень по просадке uΛu момент nepexoga переменного напряжения напряжения через ноль. Также ОН может вызывать прерывания, если результат сравнения изменился, и управлять схемой захвата таймера.

Работу встроенного аналогового компаратора можно понять, взглянув на временную диаграмму (Рис.20), на которой видно, что на инвертирующий вход подано опорное напряжение, лежащее в диапазоне (0-5)V. Если напряжение на неинверсном входе меньше опорного, то в бите АСО – 0, а если больше, то в бите АСО — 1. Этот бит находится в регистре управления компаратором

В комбинации с внешним генератором линейно изменяющегося напряжения встроенный компаратор позволяет реализовать на МК однобитный аналого-цифровой преобразователь (АЦП).

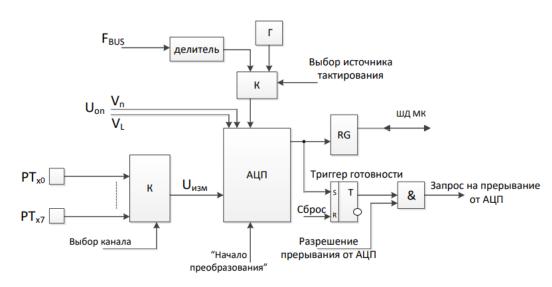

Однако более широкие возможности для работы с аналоговыми сигналами дает АЦП, встроенный в МК. Чаще всего он реализуется в виде модуля многоканального АЦП, предназначенного для ввода в МК аналоговых сигналов с датчиков физических величин и преобразования этих сигналов в двоичный код.

A----

Структурная схема типового модуля АЦП представлена на рис. 21.

Многоканальный аналоговый коммутатор К служит для подключения одного из источников аналоговых сигналов (РТх0...РТх7) ко входу АЦП. Выбор источника сигнала для преобразования осуществляется посредством записи номера канала коммутатора в соответствующие разряды регистра управления АЦП.

Два вывода модуля АЦП используются для задания опорного напряжения Uon: VH — верхний предел, VL — нижний предел. Разность потенциалов на входах VH и VL и составляет Uon. Uon = Vn – VL,

Максимальное значение опорного напряжения, как правило, равно напряжению питания МК.

Если измеряемое напряжение Uизм > Vн, результат преобразования будет равен FF. При Uизм < VL результат 00.

Разрешающая способность АЦП составляет Uon/2n, где n — число двоичных разрядов в слове результата.

Для достижения максимальной точности измерения следует выбрать максимально допустимое значение Uon.

Собственно, аналого-цифровой преобразователь выполнен по методу последовательного приближения. Практически во всех моделях 8-разрядных МК

АЦП также составляет разрядность 8 разрядов. Соответственно, формат представления результатов однобайтовый. ΑЦП Исключение измерения составляют лишь модули АЦП микроконтроллеров для преобразователями частоты электроприводов, разрешающая способность которых равна 10 разрядам. Два младших разряда результата получают с помощью дополнительного емкостного делителя, не СВЯЗОННОГО С регистром последовательного приближения.

Длительность такта преобразования задает синхронизации: генератор oguн цикл равен двум генератора tADC. Время периодам частоты ΑЦП преобразования типовых модулей ΩΛЯ микроконтроллеров составляет от единиц до десятков микросекунд.

Источником синхронизации модуля АЦП может служить встроенный РС-генератор (Г) или импульсная тактирования последовательность межмодульных магистралей MK. В первом случае частота ΑЦП обязательно синхронизации окожется оптимальной, то есть той, которая рекомендуется в техническом описании. Во втором случае выбранная по соображениям fBUS может оказаться неподходящей для модуля АЦП. На этот случай в некоторых модулей предусмотрен программируемый делитель частоты fBUS.

Момент завершения каждого цикла преобразования отмечается установкой триггера готовности данных. Если прерывания от модуля АЦП разрешены, то генерируется запрос на прерывания. Как правило, чтение регистра результата сбрасывает триггер готовности.

Большинство модулей АЦП имеют только режим программного запуска: установка одного из битов регистра режима запускает очередное измерение. Наиболее универсальные модули АЦП имеют также режим автоматического запуска, при котором после завершения одного цикла преобразования немедленно

начинается следующий. Однако данные измерения каждого цикла должны быть считаны программным способом.

Цифро-аналоговые преобразователи в составе МК большой редкостью. Функция оговогольно-одфир преобразователя реализуется программируемого таймера модуля режиме ШИМ. На одном из выводов МК формируется высокочастотная импульсная последовательность с регулируемой длительностью импульса. Полученный сигнал сглаживается фильтром нижних частот на операционном усилителе. Разрешающая способность определяется ЦАП дискретностью такого регулирования коэффициента заполнения в режиме ШИМ короткие вопросы

# 5. Для чего нужен канал входного захвата?

Канал BXOGHOSO захвата В таймерах микроконтроллеров используется RΛρ измерения временных интервалов между событиями, например, для измерения периода сигнала или длительности импульса. Канал захвата позволяет фиксировать момент точного срабатывания таймера по внешнему событию, что позволяет получать более точные данные для контроля Например, канал захвата может использован для измерения скорости вращения вала двигателя на предприятии.

# 6. Для чего нужен канал выходного сравнения?

Канал таймерах выходного сравнения В микроконтроллеров используется управления ΩΛЯ устройствами, такими внешними как светодиоды, моторы, реле и другие устройства, которые нужно включать или выключать в зависимости от состояния Как правило, канал выходного позволяет генерировать прерывание, когда значение таймера достигает заданного уровня, что позволяет

более точно контролировать время работы устройств. Также канал выходного сравнения может использоваться для реализации РWM

# 7. Чем характеризуется режим ожидания в микроконтроллерах?

Режим ожидания (sleep mode) в микроконтроллерах характеризуется низким энергопотреблением и отсутствием выполнения программных инструкций. В этом режиме микроконтроллер может находиться в течение длительного времени, пока не произойдет какое-либо событие, которое приведет к переходу в другой режим работы (например, прерывание от внешнего источника, изменение состояния входного пина и т.д.). Режим ожидания используется для экономии энергии в батарейных и портативных устройствах, а также в системах, где не требуется непрерывной работы микроконтроллера.

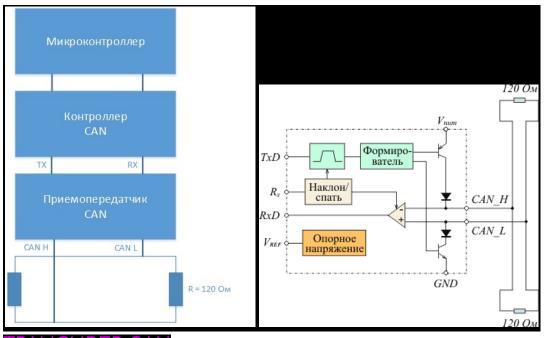

# 8. Где применяется САN-протокол?

CAN-протокол (Controller Area Network) применяется в автомобильной промышленности для передачи данных между различными электронными блоками управления автомобиля, такими как gbusamert, трансмиссия, электронная система стабилизации и т.д. Он также используется в других областях, где требуется передача скоростью, высокой данных промышленность, авиация, морская и железнодорожная техника, а также в медицине и коммуникационной оборудовании.

13. Модуль прерываний микроконтроллера. Виды прерываний; источники прерываний. Поллинг.

#### Модуль прерываний МК

Обработка прерываний в МК происходит в соответствии с общими принципами обработки прерываний в МПС. Модуль прерываний принимает запросы прерывания и организует переход к выполнению

определенной прерывающей программы. Запросы прерывания могут поступать как внешних источников, так И OTOT источников, расположенных в различных внутренних модулях МК. В качестве входов для приема запросов от внешних источников чаще всего используются выводы параллельных портов ввода/вывода, для которых эта функция является альтернативной. Источниками запросов внешних прерываний также могут быть любые изменения внешних сигналов на некоторых специально выделенных линиях портов ввода/вывода.

*Источниками* внутренних запросов прерываний могут служить следующие события:

- переполнение таймеров/счетчиков;

- сигналы от каналов входного захвата и выходного сравнения таймеров/счетчиков или от процессора событий;

- готовность памяти EEPROM;

- сигналы прерывания от дополнительных модулей МК, включая завершение передачи или приема информации по одному из последовательных портов и другие.

Любой запрос прерывания поступает на обработку, если прерывания в МК разрешены и разрешено прерывание по данному запросу. Адрес, который загружается в программный счетчик при переходе к обработке прерывания, называется "вектор прерывания". В зависимости от организации модуля прерываний конкретного МК различные источники прерываний могут иметь разные векторы или использовать некоторые из них совместно.

Вопрос о приоритетах при одновременном поступлении нескольких запросов на прерывание решается в различных МК по-разному. Есть МК с одноуровневой системой приоритетов (все запросы равноценны), многоуровневой системой с фиксированными приоритетами и многоуровневой программируемой системой приоритетов.

Если система многоуровневая, то к одному уровню могут относиться несколько запросов. Внутри одного уровня для каждого источника фиксируется его старшинство. И тогда в случае появления запросов одного уровня, очередность их обслуживания определяется с помощью внутренней процедуры - так называемого *поллинга*. Если одновременно

приняты запросы с одинаковым уровнем приоритета, обработка их будет производиться в порядке, задаваемом последовательностью внутреннего опроса флагов прерываний. Таким образом, в пределах одного приоритетного уровня существует еще одна структура приоритетов.

**Поллинг** - последовательный опрос по старшинству источников одного уровня.

Высший уровень бывает у внешних источников, а низший у последовательных источников.

Отдельно необходимо описать аппаратные прерывания, связанные с включением питания, подачей сигнала "сброс" и переполнением сторожевого таймера. Они имеют немаскируемый характер и чаще всего разделяют один общий вектор прерывания. Это вполне логично, поскольку результатом каждого из событий является начальный сброс МК.

14. Режимы энергопотребления в микроконтроллерах: активный, ожидания, останова. Мощность потребления; группы микроконтроллеров по величине напряжения питания.

Малый уровень энергопотребления является зачастую определяющим фактором при выборе способа реализации цифровой управляющей системы. Современные МК предоставляют пользователю большие возможности в плане экономии энергопотребления и имеют, как правило, следующие о*сновные режимы работы*:

- 1) активный режим (Run mode) основной режим работы МК. В этом режиме МК исполняет рабочую программу, и все его ресурсы доступны. Потребляемая мощность имеет максимальное значение PRUN. Большинство современных МК выполнено по КМОП-технологии, поэтому мощность потребления в активном режиме сильно зависит от тактовой частоты;

- 2) режим ожидания (Wait mode, Idle mode или Halt mode холостой ход). В этом режиме прекращает работу центральный процессор, но продолжают функционировать периферийные модули, которые контролируют состояние объекта управления. При необходимости сигналы

от периферийных модулей переводят МК в активный режим, и рабочая программа формирует необходимые управляющие воздействия. Перевод МК из режима ожидания в рабочий режим осуществляется по прерываниям от внешних источников или периферийных модулей, либо при сбросе МК. В режиме ожидания мощность потребления МК PWAIT снижается по сравнению с активным режимом в 5...10 раз; PRUN=(5-10)PWAIT.

3) режим останова (Stop mode, Sleep mode или Power Down mode, режим микропотребления). В этом режиме прекращает работу как центральный процессор, так и большинство периферийных модулей. Приостанавливается выполнение всех функций, т.к. прекращает работать синхрогенератор. Значения регистров специальных функций теряется, но сохраняется содержимое ОЗУ. Переход МК из состояния останова в рабочий режим возможен, как правило, только по прерываниям от внешних источников или после подачи сигнала сброса. В режиме останова мощность потребления МК РЅТОР снижается по сравнению с активным режимом примерно на три порядка и составляет единицы микроватт: PRUN ≈ 10³ PЅТОР.

Два последних режима называют режимами пониженного энергопотребления. *Минимизация* энергопотребления системы на МК достигается за счет оптимизации мощности потребления МК в активном режиме, а также использования режимов пониженного энергопотребления. При этом необходимо иметь в виду, что режимы ожидания и останова существенно отличаются временем перехода из режима пониженного энергопотребления в активный режим. Выход из режима ожидания обычно происходит в течение 3...5 периодов синхронизации МК, в то время как задержка выхода из режима останова составляет несколько тысяч периодов синхронизации. Кроме снижения динамики работы системы значительное время перехода в активный режим является причиной дополнительного расхода энергии.

4) Еще один режим пониженного энергопотребления - экономичный режим (Power save) – в AVR. Продолжает работать только генератор таймера, временная база сохраняется, все остальные функции выключены.

В зависимости от диапазона питающих напряжений все МК можно разделить на *три основные группы*:

- МК с напряжением питания 5,0 В±10%. Эти МК предназначены, как правило, для работы в составе устройств с питанием от промышленной или бытовой сети, имеют развитые функциональные возможности и высокий уровень энергопотребления.

- ІМК с расширенным диапазоном напряжений питания: от 2,0...3,0 В до 5,0-7,0 В. МК данной группы могут работать в составе устройств как с сетевым, так и с автономным питанием.

- МК с пониженным напряжением питания: от 1,8 до 3 В. Эти МК предназначены для работы в устройствах с автономным питанием и обеспечивают экономный расход энергии элементов питания

- 15. Способы задания тактовой частоты микроконтроллеров. Виды времязадающих элементов, их характеристики. Структурная схема системы синхронизации на примере микроконтроллеров AVR фирмы Atmel. Какие могут быть источники тактового сигнала?

На практике используются три основных способа задания тактовой частоты генератора: с помощью кварцевого резонатора, керамического резонатора и внешней RC-цепи.

В качестве времязадающих можно использовать емкостно-резисторные или индуктивно-резисторные линейные формирующие цепи, линии колебательные задержки И контуры. В большинстве генераторов импульсов в качестве времязадающих используются RC - цепи, что простотой объясняется И технологичностью изготовления. Индуктивно-резисторные цепи и колебательные LC-контуры используются существенно реже и в основном в генераторах импульсов на активных двухполюсниках, что объясняется плохой технологичностью катушек индуктивности.

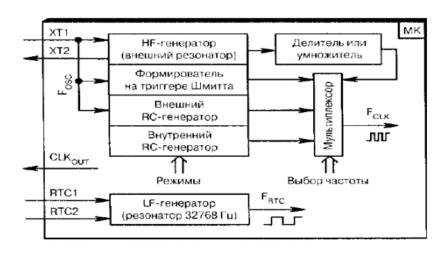

Обобщенная структурная схема MK AVR приведена на рис.63.

Для того чтобы МК заработал, необходимо подать на ЦПУ тактовые импульсы. Чем выше их частота, тем быстрее выполняются операции, а чем ниже их частота, тем меньше потребление тока. Формированием тактовых частот занимается подсистема синхронизации (рис.22). На её структурной схеме имеется несколько встроенных генераторных узлов. Расшифровка сокращений: НF (High Frequency) — высокочастотный, LF (Low Frequency) — низкочастотный, CLK (CLocK) — тактирование.

Рис.22

#### Источники синхронизации

- Внешний кварцевый/керамический резонатор

- Внешний низкочастотный кварцевый резонатор

- Внешний RC-генератор

- Встроенный калиброванный RC-генератор

- Внешняя синхронизация

16. Аппаратные средства обеспечения надежной работы микроконтроллеров. Типовые схемы формирования сигнала сброса. Блок детектирования пониженного напряжения питания. Подсистема начального сброса на примере микроконтроллеров AVR фирмы Atmel.

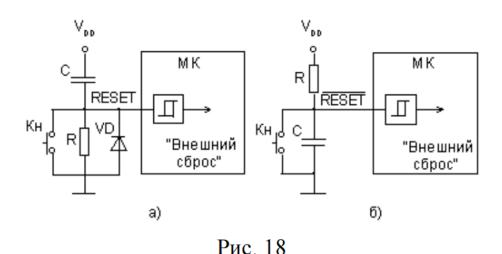

Типовые схемы формирования сигнала внешнего сброса для МК с высоким активным уровнем сигнала сброса (а) и низким активным уровнем сигнала сброса (б) представлены на рис. 18.

#### Блок детектирования пониженного напряжения питания

В реальных условиях эксплуатации может сложиться такая ситуация, при которой напряжение питания МК опустится ниже минимально допустимого, но не достигнет порога отпускания схемы РОR. В этих условиях МК может "зависнуть". При восстановлении напряжения питания до номинального значения МК останется неработоспособным.

Для восстановления работоспособности системы после "просадки" напряжения питания МК необходимо снова сбросить. Для этой цели в

современных МК реализован дополнительный блок детектирования пониженного напряжения питания. Такой модуль используется в МК семейства НС08 фирмы Motorola, аналогичный модуль имеется в составе семейства PIC17 фирмы Microchip. Рассматриваемый модуль отслеживает изменение напряжения питания и при его снижении до уровня чуть ниже минимально допустимого генерирует сигнал внутреннего сброса. Когда напряжение питания возрастет до порогового, запускается таймер задержки сброса. После задержки сигнал внутреннего сброса снимается, и происходит запуск МК. Уровень срабатывания блока детектирования пониженного напряжения питания значительно превышает напряжение сохранения данных в ОЗУ МК. Событие сброса по сигналу блока пониженного напряжения питания отмечается специальным битом в одном из регистров МК. Следовательно, программно анализируя этот бит после сброса МК, можно установить, что данные целы, и продолжить выполнение программы.

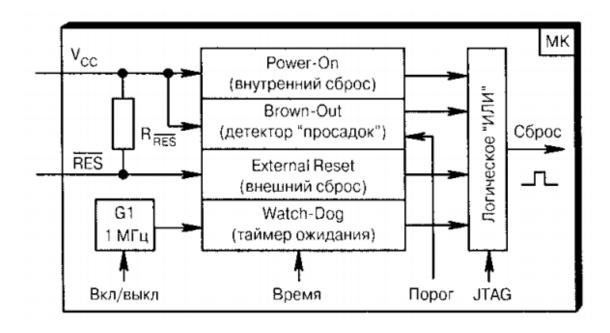

На рис.19 показана *подсистема начального сброса микроконтроллеров* AVR семейств ATmega, ATtiny. Схема включает модуль мониторинга напряжения питания и сторожевой таймер:

Рис.19

Источники сброса:

- Power-On внутренний автоматический сброс, который активизируется сразу после подачи питания;

- Brown-Out сброс от внутреннего детектора «просадок» питающего напряжения;

- External Reset внешний сброс НИЗКИМ уровнем на выводе ; ·

- Watch-Dog сброс от внутреннего «сторожевого» таймера при случайной остановке работы ЦПУ или зависании программы;

- JTAG программный сброс через отладочный интерфейс JTAG.

Все источники сброса равноценны, что подчёркивает логический элемент «ИЛИ», находящийся внутри MK. Установка режимов сброса производится конфигурационными битами, также a программно-доступными регистрами из области SFR. Настраиваться могут: порог срабатывания детектора «просадок» напряжения, длительность времени задержки таймера ожидания Watch-Dog, моменты включения/отключения генератора G1. При наступлении одного из формируется перечисленных событий внутренний сигнал все регистры ввода/вывода заносятся их ВЫСОКОГО уровня, во начальные значения, а в счетчик команд загружается значение \$000 (адрес вектора сброса).

Одновременно запускается таймер формирования задержки сброса. По истечении определенного промежутка времени (предполагается, что за это время микроконтроллер перейдет в определенное устойчивое состояние) внутренний сигнал сброса переводится в НИЗКИЙ уровень

Там очень много, все вставлять не буду(можно прочитать в пункте 3.5.3)

#### короткие вопросы

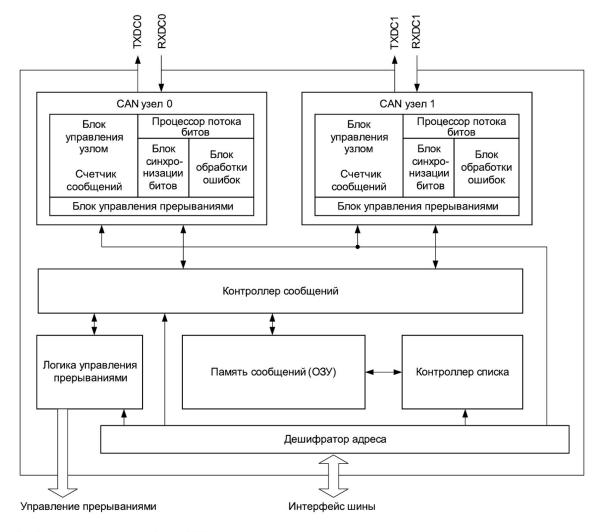

9. Что такое bit staffing в CAN-протоколе?

#### Методы обнаружения ошибок.

CAN протокол определяет пять способов обнаружения ошибок в сети:

- Bit monitoring

- ACKnowledgement Check

- Bit stuffing

- CRC Check

- Frame check

- Разрядная ошибка **Bit monitoring** появляется, когда передатчик

#### 10. Чем характеризуется режим ШИМ?

В ШИМ в качестве ключевых элементов используют транзисторы (могут быть применены и другие полупроводниковые приборы), работающие не в линейном, а в ключевом режиме, то есть транзистор всё время либо разомкнут (выключен), либо замкнут (находится в состоянии насыщения).

В режиме ШИМ на соответствующем выводе МК формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы. Длительность импульса прямо пропорциональна коду в регистре данных канала.

# 17. Задачи, решаемые с помощью модулей контроллеров последовательного вводавывода? Классификация интерфейсов последовательного ввода-вывода?

которые решаются средствами модуля контроллера последовательного ввода/вывода, можно разделить на три основные 1)связь встроенной микроконтроллерной группы: системы с системой управления верхнего уровня, например, С персональным компьютером(RS-232C и RS-485); 2)связь с внешними по отношению к МК периферийными ИС. а также с датчиками физических величин с последовательным выходом(I2C, SPI), а также нестандартные протоколы обмена;

3)интерфейс связи с локальной сетью в мультимикроконтроллерных системах.

В системах с числом МК до пяти обычно используются сети на основе интерфейсов I2C, RS-232C и RS-485 с собственными сетевыми протоколами высокого уровня.

С точки зрения организации обмена информацией упомянутые типы интерфейсов последовательной связи отличаются режимом передачи данных (синхронный или асинхронный), форматом кадра (число бит в посылке при передаче байта полезной информации) и временными диаграммами сигналов на линиях.

Число линий, по которым происходит передача в последовательном коде, обычно равно двум (I2C, RS-232C, RS-485) или трем (SPI, некоторые нестандартные протоколы). Данное обстоятельство позв-т спроектировать модули контроллеров послед-го обмена таким образом, чтобы с их помощью на аппаратном уровне можно было реализовать несколько типов последовательных интерфейсов. При этом режим передачи и формат кадра поддерживаются на уровне логических сигналов, а реальные физические уровни сигналов для каждого интерфейса получают с помощью специальных

ИС, которые называют приемопередатчиками, конверторами, трансиверами. Среди различных типов встроенных контроллеров последовательного обмена, которые входят в состав тех или иных 8-разрядных МК, сложился стандарт «де-факто» — модуль UART (Universal Asynchronous Receiver and Transmitter). UART — это универсальный асинхронный приемопередатчик. Однако большинство модулей UART, кроме асинхронного режима обмена, способны также реализовать режим синхронной передачи данных. Модули типа UART в асинхронном режиме работы позволяют реализовать протокол обмена для интерфейсов RS-232C, RS-422A, RS-485, в синхронном режиме — нестандартные синхронные протоколы обмена, и в некоторых моделях.

#### Классификация, еще раз:

Интерфейсы характеризуются следующими параметрами:

- 1) пропускной способностью интерфейса количеством информации, которая может быть передана через интерфейс в единицу времени;

- 2) максимальной частотой передачи информационных сигналов через интерфейс;

- 3) информационной шириной интерфейса числом бит или байт данных, передаваемых параллельно через интерфейс;

- 4) максимально допустимым расстоянием между соединяемыми устройствами;

- 5) динамическими параметрами интерфейса временем передачи отдельного слова или блока данных с учетом продолжительности процедур подготовки и завершения передачи;

- 6) общим числом проводов (линий) в интерфейсе.

В настоящее время не существует однозначной классификации интерфейсов. Можно выделить следующие четыре классификационных признака интерфейсов:

- способ соединения компонентов системы (радиальный, магистральный, смешанный);

- способ передачи информации (параллельный, последовательный, параллельно-последовательный);

- принцип обмена информацией (асинхронный, синхронный);

- режим передачи информации (двусторонняя поочередная передача, односторонняя передача).

- 18. Последовательный обмен в МП-системах с помощью модуля UART. Структурная схема модуля UART, ее основные элементы. Передача и прием данных модулем

# UART. В каком случае могут возникнуть ошибки при считывании данных в микроконтроллер?

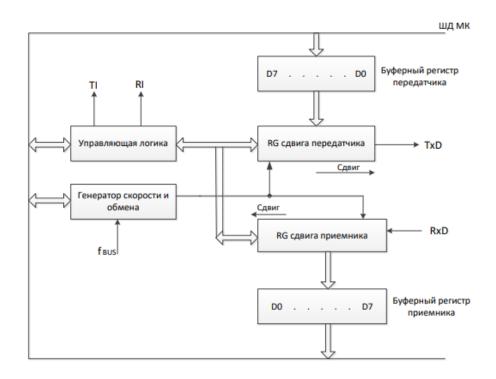

Среди различных встроенных контроллеров типов последовательного обмена, которые входят в состав тех или иных 8-разрядных МК, сложился стандарт "де-факто" модуль UART (Universal Asynchronous Receiver Transmitter). UART and универсальный асинхронный приемопередатчик, работающий дуплексном режиме. Несмотря на то, что в названии отсутствует упоминание о синхронном обмене, в большинстве подобных модулей он, тем не менее, реализован. Однако это название не является единственным, и некоторые производители МК используют свои имена: USART -Universal Synchronous/Asynchronous Receiver and Transmitter, SCI – Serial Communication Interface, USI – Universal Serial Interface и др. Модули типа UART в асинхронном режиме работы позволяют реализовать протокол обмена для интерфейсов RS-232C, RS-422A, RS-485, в синхронном режиме — нестандартные синхронные протоколы обмена, и в некоторых моделях SPI. Асинхронная передача данных. При асинхронной последовательной передаче, структура организации которой показана на рис. 29, между передатчиком и приемником нет линии синхронизации, импульсы на которой выделяли моменты передачи отдельных битов, и передача информационного слова может производиться асинхронно, в любой произвольный момент времени.

Структурная схема:

В модуле используется двойная буферизация, его структура содержит 2 независимые подсистемы — приемник и передатчик, поэтому возможен режим одновременного приема и передачи информации.

Основу каждой подсистемы составляют последовательный сдвиговый регистр и параллельный регистр буфера данных. Буферные регистры приемника и передатчика отображаются в памяти МК одним адресом, но при записи данные помещаются в буфер передатчика, а при чтении считываются из буфера приемника. Для настройки модуля устанавливаются некоторые биты в управляющих регистрах.

#### Передача данных от микроконтроллера к другим устройствам.

В отсутствие передачи на линии всегда обеспечивается уровень сигнала, соответствующий логической 1. Для передачи байт данных записывается в буферный регистр передатчика. Если передача разрешена, содержимое буферного регистра загружается в регистр сдвига передатчика.

Передача каждого кадра начинается посылкой стартового бита (изменением значения сигнала в линии из 1 в 0 на один период стробирующих сигналов). Генератор скорости обмена управляет сдвиговым регистром, и биты из него последовательно, начиная с младшего D0, передаются на выход TxD. Если в процессе обмена производится контроль по четности, то затем передается бит четности. В

завершение посылается стоп-бит, и линия данных в течение одного такта находится в состоянии простоя.

По завершении передачи байта данных устанавливается в «1» бит ТІ, т.е. буфер пуст и в него могут загружаться новые данные. Бит ТІ м.б. считан программно и генерируется запрос на прерывание, если прерывания от передатчика в МК разрешены. Старт-бит следующего кадра посылается в любой момент после стоп-бита, то есть между передачами возможны паузы произвольной длительности.

#### Прием данных в микроконтроллер.

Если работа приемника разрешена, распознается стартовый бит, передний фронт которого используется в приемнике как признак начала кадра и как начало отсчета времени для определения моментов прихода отдельных битов в кадре. Затем приемник начинает процедуру приема и подсчета принимаемых битов. Данные поступают на вход RxD в последовательном коде, причем для получения достоверных значений битов в период стробирования производится несколько считываний состояния линии и решение принимается по мажоритарному принципу, например, при трехкратном считывании – два из трех. Процедура завершается с приходом стоп-бита занесением результата в буферный регистр приемника. Флаг завершения приема RI устанавливается в «1». Бит RI м.б. считан программно и генерируется запрос на прерывание, если прерывания от приемника разрешены. В подпрограмме прерывания байт данных из буферного регистра считывается в память МК. После копирования байта данных из сдвигового регистра в буферный приемник может сразу формировать новый байт данных последовательно поступающий на вход RxD. Необходимо, чтобы МК успел сосчитать данные в свою память до завершения формирования следующего байта в сдвиговом регистре.

Если этого не произойдет, новый байт может затереть старый, и произойдет ошибка записи (в MSC-51). В МК фирмы Motorola имеется защита: устанавливается в «1» флаг ошибки (OR=1 Overrun), который может генерировать запрос на прерывание от приемника.

19. Типы кадров асинхронного обмена, предусмотренные модулем UART. Структурная схема локальной сети, осуществляющей связь микроконтроллеров с помощью UART. Принципы обмена между ведущим и ведомым микроконтроллерами. Структура пакета обмена.

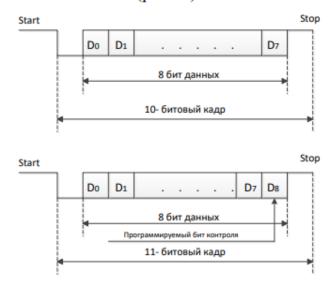

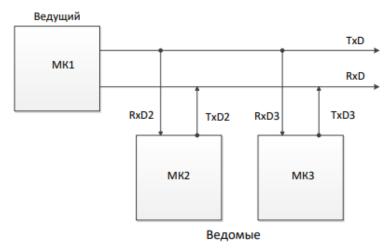

Все модули типа UART предусматривают два кадра асинхронного обмена – 10-битовый и 11-битовый (рис.30).

Для обмена в многопроцессорной системе используется 11-битовый формат кадра. Каждый микроконтроллер в системе имеет свой сетевой адрес. При организации обмена передающий микроконтроллер (МК1) играет роль ведущего, а принимающие (МК2, МК3) - роль ведомых. Обмен между ведущим и ведомыми осуществляется пакетами, включающими не менее трех 11 битовых кадров. Первый кадр - адрес ведомого микроконтроллера. Признак адреса D8=1. Затем может посылаться несколько кадров данных, для обмена с ведомым микроконтроллером (разряд D8=0). Последний кадр должен содержать 11 нулевых битов, включая стоповый.

Порядок обмена.

1.До начала обмена в управляющем регистре должен быть установлен в единицу флаг разрешения обмена (SM2=1). Тогда кадр адреса

будет вызывать прерывание, а кадр данных - нет. Вид информации - адрес или данные определяется по значению бита D8.

- 2.В исходном состоянии приемники всех ведомых микроконтроллеров находятся в ожидании.

- 3. Ведущий посылает всем ведомым одновременно первый кадр пакета обмена, в котором D0 D7 адрес, D8=1.

- 4. Все ведомые принимают этот кадр, выходят из состояния ожидания, формируют запрос на прерывание и в подпрограмме обработки прерывания анализируют принятый адрес, сравнивая его с собственным сетевым.

- 5. При идентификации своего адреса ведомый микроконтроллер сбрасывает бит SM2 и читает данные от ведущего, сопровождаемые признаком D8=0. Остальные ведомые снова переходят в режим ожидания, оставляют свои биты SM2=1 и продолжают выполнять текущую программу. Данные от ведомого может принимать и ведущий.

- 6. Обмен завершается 11-битовым нулевым кадром. Для сброса в «0» стопового бита ведущий формирует сигнал «break». В ответ ведомый вновь переводит свой приемник модуля UART в состояние ожидания, устанавливая бит SM2=1. Сеть вновь готова к передаче следующего пакета.

Последовательный порт является источником 3-х видов внутренних прерываний:

- 1)Когда буфер приема полон и разрешено прерывание от приемника.

- 2)Когда буфер передачи пуст и разрешено прерывание от передатчика.

- 3)Прерывание по ошибке (когда в буфер приема поступает очередной символ до того, как процессор считывает предыдущий).

В некоторых семействах МК вектор прерывания UART один и для приема и для передачи, поэтому для определения источника прерывания в подпрограмме обслуживания производится программный опрос состояния флагов приема RI и передачи ТІ. В этом случае флаги RI и ТІ не сбрасываются автоматически при входе в подпрограмму обслуживания, а их сброс производится только после определения того, каким событием вызвано прерывание – приемом или передачей.

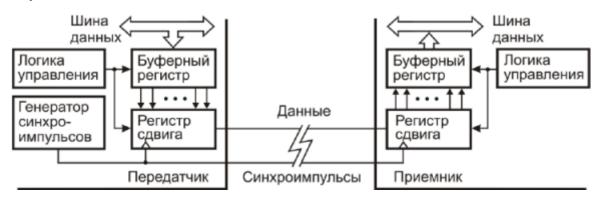

Последовательный порт может работать и в синхронном режиме

Способ синхронной передачи данных предполагает синхронизацию работы приемника и передатчика посредством включения тактовой

информации в передаваемый сигнал или, чаще всего, путем использования общей для источника и приемника линии синхронизации, импульсы на которой служат для выделения отдельных битов в канале.

Структура организации синхронной передачи данных показана на рис. 33.

Начало передачи инициируется занесением передаваемых данных в буферный регистр передатчика, затем передатчик загружает информацию в сдвиговый регистр, запускает генератор синхроимпульсов и счетчик. Синхроимпульсы передаются по линии TxD. С каждым синхронизирующим сигналом данные сдвигаются на одну позицию и поступают на линию данных RxD.

При этом каждый передаваемый бит данных сопровождается импульсом по линии синхронизации, информирующим приемник о наличии на линии данных информационного бита. Приемник состоит из регистра сдвига с последовательной записью, счетчика и логической схемы, которые управляются теми же синхросигналами. После того как поступление необходимого счетчик зарегистрирует количества синхросигналов (и, соответственно, бит данных), инициирует параллельную передачу полученных данных из сдвигового регистра в буферный регистр приемника данных, откуда они могут быть считаны для дальнейшей обработки в прикладной программе.

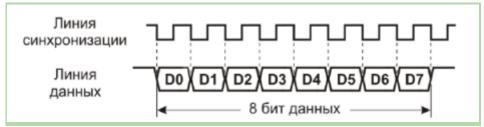

20. Последовательный интерфейс SPI. Структурная схема сети. Обмен в стандарте SPI; обобщенные временные диаграммы.

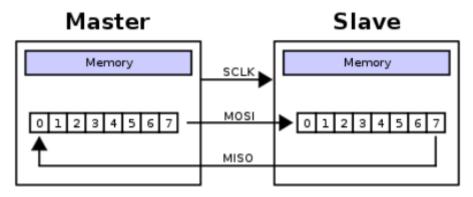

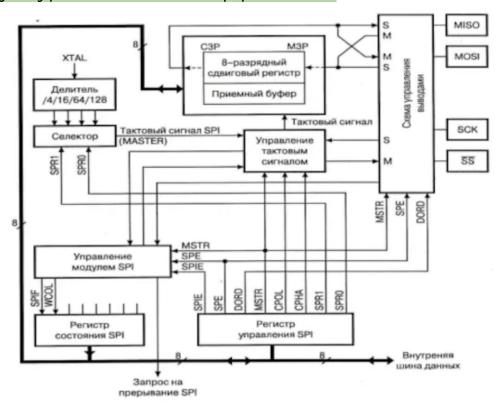

SPI (Serial Peripheral Interface SPI bus— последовательный периферийный интерфейс, шина SPI)— последовательный синхронный стандарт передачи данных в режиме полного дуплекса, предназначенный для обеспечения простого и недорогого высокоскоростного сопряжения микроконтроллеров и периферии. Стандарт был предложен фирмой Motorola для связи микроконтроллера с периферийными устройствами микропроцессорной системы, которые располагаются на одной плате с микроконтроллером. Это могут быть простейшие устройства, такие как сдвиговые регистры, так и сложные интегральные схемы со встроенными управляющими контроллерами, например, ЦАП, ОЗУ, ЗУ типа FLASH, EEPROM.

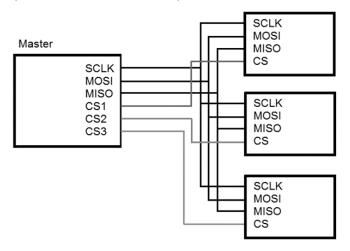

В SPI всегда есть один ведущий и один/несколько ведомых. SPI синхронным интерфейсом, В котором любая передача синхронизирована с общим тактовым сигналом, генерируемым ведущим (процессором). Принимающая устройством (ведомая) периферия синхронизирует получение битовой последовательности с тактовым сигналом. К одному последовательному периферийному интерфейсу микросхемы может присоединяться несколько ведущего устройствамикросхем. Ведущее устройство выбирает ведомое для активируя сигнал «выбор кристалла» на ведомой микросхеме. Периферия, не выбранная процессором, не принимает участия в передаче по SPI.

В SPI используются четыре цифровых сигнала:

MOSI- линия передачи данных от ведущего к ведомому (Master Output Slave Input);

MISO- линия передачи от ведомого к ведущему (Master Input Slave Output);

SCLK или SCK- линия стробирования данных (синхроимпульс);

SS1, SS2, SS3, SS или CS (Chip Select, Slave Select) - линии выбора ведомого устройства.

В ведущем режиме к выводу MOSI подключается выходная линия, а к MISO – входная, SCK – выход. В ведомом режиме выводы меняются ролями, SCK – вход.

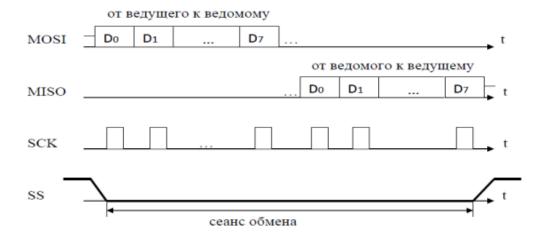

Рассмотрим принцип обмена данными в стандарте SPI. Временная диаграмма этого процесса приведена на рис.37. Передача осуществляется пакетами. Длина пакета, как правило, составляет 1 байт (8 бит). Цикл связи всегда инициирует ведущее устройство установкой низкого уровня на выводе выбора подчиненного устройства (SS). Подлежащие передаче данные ведущее и ведомое устройства помещают в сдвиговые регистры.

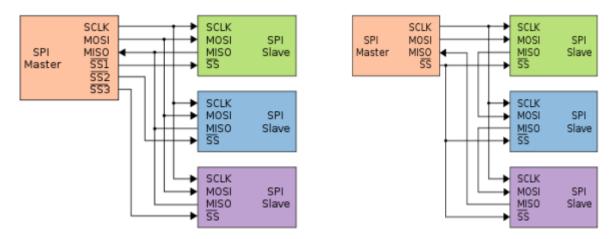

Интерфейс SPI позволяет подключать к одному ведущему устройству несколько ведомых устройств, причем подключение может быть осуществлено несколькими способами. На рис. 38 приведены две микроконтроллерные системы, использующие модуль SPI: а) с радиальной структурой связи; б) с кольцевой структурой связи.

#### короткие вопросы

# 11. Какая архитектура процессора у микроконтроллеров семейства PIC?

Микроконтроллеры PIC имеют RISC-архитектуру. RISC – сокращённый набор команд, используется также в процессорах для мобильных устройств.

#### 12. Структурная схема интерфейса SPI.

21. Модуль последовательного синхронного интерфейса SPI. Структурная схема; выбор режимов работы. Последовательность обмена между ведущим и ведомым устройствами

SPI (Serial Peripheral Interface) последовательный синхронный стандарт передачи данных в режиме полного дуплекса, предназначенный для обеспечения простого и недорогого высокоскоростного сопряжения

<u>Структура</u> мастер и факинг слейвы

SPI обеспечивает связь между микроконтроллером (мастером) и одним или несколькими периферийными устройствами (рабами). Основные компоненты:

- 1. <u>Микроконтроллер</u> (Master): Микроконтроллер играет протоколе SPI. Он инициирует роль мастера между собой контролирует передачу данных устройствами. Мастер периферийными управляет сигналами тактовой частоты (SCK), выборки данных (MOSI) передачи данных u линии выбора устройства (SS) для каждого раба.

- 2. <u>Периферийные устройства</u> (Slaves): Периферийные устройства являются рабами в протоколе SPI. Они подключаются к мастеру и обмениваются данными по его командам. Каждое периферийное устройство имеет свою собственную линию выбора (SS), которая используется мастером для выбора конкретного раба во время передачи данных.

- <u>Линия выбора устройства (SS):</u> 3. Линии выбора выбора устройства используются мастером ΩΛЯ конкретного раба перед передачей данных. Macmep соответствующую выбора активирует линию устройства, чтобы указать, с каким рабом он хочет обмениваться данными.

- 4. <u>Сигналы SCK, MOSI и MISO</u>: Сигнал SCK (Serial Clock) представляет собой тактовый сигнал, используемый для синхронизации передачи данных между мастером и рабами. Сигнал MOSI (Master Out Slave In) представляет собой линию передачи данных от мастера к рабу, а сигнал MISO (Master In Slave Out) представляет собой линию передачи данных от раба к мастеру.

- 5. Регистры данных и сдвизовые регистры: Микроконтроллер u периферийные устройства содержат регистры данных для временного хранения передаваемых и принимаемых данных. Они могут быть буферизации использованы ΩΛЯ аанных последовательной передачи по линиям MOSI и MISO с использованием тактового сигнала SCK.

Сигналы тактирования, передачи и выбора устройства периферийные контролируются мастером, a устройства мастера реагируют на команды передают данные обратно. Это позволяет эффективно обмениваться данными между микроконтроллером и устройствами, подключенными периферийными no интерфейсу SPI.

Режимы работы определяет способ передачи данных и синхронизацию между ведущим и ведомым устройствами. Основные режимы работы:

1. Режим 0 (CPOL = 0, CPHA = 0): В этом режиме линия SCK (тактовый сигнал) в состоянии покоя (CPOL = 0) имеет низкий уровень, а данные считываются на фронте сброса (СРНА = 0) тактового сигнала. Данные

передаются на фронте установки SCK и считываются на фронте сброса SCK.

- 2. Режим 1 (CPOL = 0, CPHA = 1): В этом режиме линия SCK в состоянии покоя имеет низкий уровень, а данные считываются на фронте установки SCK. Данные передаются на фронте сброса SCK и считываются на фронте установки SCK.

- 3. Режим 2 (CPOL = 1, CPHA = 0): В этом режиме линия SCK в состоянии покоя имеет высокий уровень, а данные считываются на фронте сброса SCK. Данные передаются на фронте установки SCK и считываются на фронте сброса SCK.

- 4. Режим 3 (CPOL = 1, CPHA = 1): В этом режиме линия SCK в состоянии покоя имеет высокий уровень, а данные считываются на фронте установки SCK. Данные передаются на фронте сброса SCK и считываются на фронте установки SCK.

CPOL (Clock Polarity) определяет уровень, который принимает линия SCK в состоянии покоя, а CPHA (Clock Phase) определяет момент считывания и передачи данных относительно тактового сигнала SCK.

# Последовательность обмена между ведущим и ведомым

Ведущий (микроконтроллера) Ведомый (периферийное устройство)

- 1. Микроконтроллер (ведущее устройство) активирует линию выбора устройства (SS) для выбранного ведомого устройства, устанавливая ее в низкий уровень.

- 2. Мастер генерирует тактовый сигнал (SCK), определяющий скорость передачи данных.

- 3. Мастер подает данные на линию MOSI (Master Out Slave In), которые он хочет передать ведомому устройству.

- 4. Ведомое устройство получает данные с линии MOSI и обрабатывает их соответствующим образом.

- 5. В то же время ведомое устройство может передавать данные мастеру на линии MISO (Master In Slave Out).

- 6. Мастер считывает данные с линии MISO.

- 7. Процесс передачи данных повторяется для каждого бита или байта, пока все данные не будут переданы или получены.

- 8. По завершении передачи данных мастер деактивирует линию выбора устройства (SS), устанавливая ее в высокий уровень.

Обмен данными в протоколе SPI осуществляется синхронно, с использованием тактового сигнала SCK.

Важно отметить, что каждое ведомое устройство в сети SPI должно иметь свою собственную линию выбора устройства (SS). Мастер активирует нужную линию выбора для выбора конкретного ведомого устройства перед передачей данных. Это позволяет мастеру общаться с несколькими ведомыми устройствами в одной сети SPI.

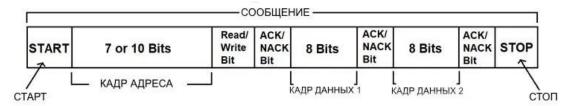

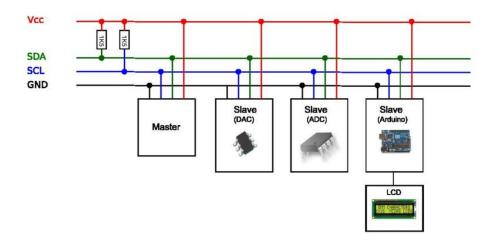

- 22. Двухпроводной последовательный интерфейс I2C: типовая структурная схема; основные свойства. Логическая схема подключения устройств к шине I2C. Какое устройство генерирует синхросигналы? Доминантный и рецессивный логические уровни на шине I2C. Временные диаграммы формирования сигналов «СТАРТ», «СТОП» и передачи данных для шины I2C.

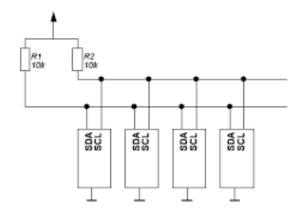

- IIC I2C Inter-Integrated Circuit последовательная асимметричная шина для связи между интегральными схемами внутри электронных приборов.

- В <u>структуре</u> интерфейс I2C использует две линии для связи между устройствами: линию данных (SDA) и линию тактирования (SCL). Оба сигнала являются двунаправленными.

- 1. SDA (Serial Data Line): Линия данных используется для передачи информации между устройствами. Каждое устройство, подключенное к шине I2C, может выступать в роли передатчика или приемника данных. Линия SDA управляется только ведущим устройством (Master).

- 2. SCL (Serial Clock Line): Линия тактирования является сигналом тактирования, синхронизирующим передачу данных по линии SDA. Линия SCL также управляется только ведущим устройством.

- 3. I2C Bus: Шина I2C представляет собой физическую среду, по которой передаются сигналы SDA и SCL. Устройства, подключенные к шине, должны иметь уникальные адреса, чтобы быть идентифицированными.

# <u>Основные свойства</u>: